# ENGS 31 Final Project Report: The Calculator

# Gavin Burns and Sarah Hutchinson

August 2021

#### Abstract

The goal of our project was to use digital electronic design to create a calculator that can add, subtract, multiply, and divide numbers with results up to 3 digits. Our resulting design uses a computer-connected universal asynchronous receiver-transmitter system (UART) to send signals to the FPGA, where the calculations take place. The calculation process and results are outputted to the 7-segment display on the FPGA, with additional features such as LEDs to indicate which step of the entry process is occurring, and buttons to view past operand entries.

# Contents

| 1        | Introduction               | 3 |  |  |  |

|----------|----------------------------|---|--|--|--|

| <b>2</b> | Design Solution            | 3 |  |  |  |

|          | 2.1 Specifications         | 3 |  |  |  |

|          | 2.2 Operating Instructions | 3 |  |  |  |

|          | 2.2.1 Setup                | 3 |  |  |  |

|          | 2.2.2 Communicating        |   |  |  |  |

|          | 2.2.3 Display              |   |  |  |  |

|          | 2.3 Theory of Operation    |   |  |  |  |

|          | 2.3.1 Top Level Design     |   |  |  |  |

|          | 2.3.2 UART                 |   |  |  |  |

|          | 2.3.3 ASCII Converter      | 5 |  |  |  |

|          | 2.3.4 Main Controller      |   |  |  |  |

|          | 2.3.5 Main Datapath        |   |  |  |  |

|          | 2.3.6 Math Block           |   |  |  |  |

|          | 2.3.7 Binary to BCD        |   |  |  |  |

|          | 2.3.8 Display              |   |  |  |  |

| 3        | Evaluation                 | 7 |  |  |  |

| J        | 3.1 Functionality          |   |  |  |  |

|          | 3.2 Review                 |   |  |  |  |

|          | 5.2 Review                 | 0 |  |  |  |

| 4        | Conclusions                |   |  |  |  |

| 5        | Acknowledgements           | 8 |  |  |  |

| 6        | References                 | 8 |  |  |  |

#### 1 Introduction

For our final project in ENGS31 we were tasked with designing a hardware calculator in VHDL. Specifically, we wanted a calculator that could represent integers between -999 to 999, carry the four main mathematical operations(+ - \* /), and be able to recursively apply answers to the next equation. Using processes and ideas we've learned throughout the term we came up with a thorough design and began working. Over the course of the project we practiced top-down circuit design and many different debugging techniques. Furthermore, we added some ease of life capabilities and additive features to separate our design from a simple calculator.

# 2 Design Solution

#### 2.1 Specifications

Our calculator takes inputs coming from a connected computer, manipulates entered values and operators within the FPGA (calculator functions), and outputs values and results onto the FPGA seven-segment display. Values come into the system through a universal asynchronous receiver-transmitter (UART) system. This is a form of serial input. Using the Waveforms application on the computer, we enter numbers and operators which are then sent to the FPGA, coded as an ASCII code in serial. Our calculator connected to the computer via Analog Discovery 2 (transmits signal). Data is sent from the computer at a baud rate of 115.2k. This rate refers to how many different signals occur per second. This is relevant because since the UART is asynchronous, a clock signal is not sent to the FPGA and therefore it is necessary to use the baud rate to determine how to read the incoming signal. Our system is clocked at 1MHz, which means that a new signal is sent from the computer approximately every 8 clock cycles. Our calculator outputs to the 7-segment display on the FPGA, as well as to the LED lights. Depending on what part of the calculation process is occurring, either the operands, a decimal point to indicate which operator is in use, or the answer is displayed on the board. One of four LED lights illuminates at any given time to indicate which part of the calculation is occurring and what the next entry should be from the user (waiting for operand, waiting for operator, showing answer, or overflow). Additionally, there are input buttons on the FPGA which can be pressed to view past operands on the 7-segment display.

## 2.2 Operating Instructions

#### 2.2.1 Setup

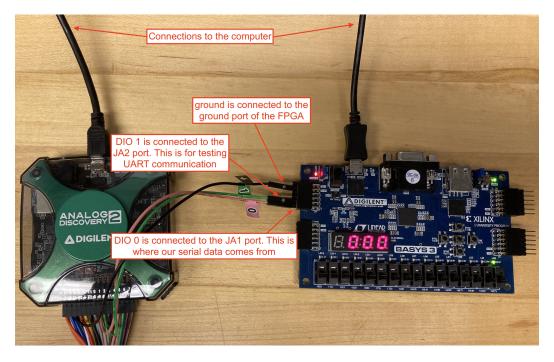

Figure 1: AD2 and FPGA connections. DIO 0(pink) and 1(green) are used to send and receive signals from the AD2 to FPGA respectively. Additional connections are made individually between the Ad2 and FPGA to the computer. Signals are typed in via a keyboard, sent though the AD2 and finally delivered to the FPGA vai serial data.

In order to operate our calculator it is important to understand how to set it up. Since we are using a FPGA and AD2 converter we'll need to connect the data ports together to communicate between them. According to out constraints file in the Appendix, we will be using the DIO 0 and DIO 1 wires on the AD2 to control the transmission and receiving of signals respectively. On our FPGA, the JA1 port is where our serial data from the computer comes from, so we'll connect the DIO 0(pink cable) wire to the JA1 port. Likewise, the JA2 port is the transmission port of our FPGA back to the AD2 and computer moniter. Although we used this port for checking UART capabilities and debugging you can connect the this port to the DIO 1 wire as shown in the figure above. Do not forget to also connect the ground wire of the AD2 to the any ground port on the FPGA. For ease of use we used the ground port closest to the AD2 (JA5).

Lastly, the micro USB ports for both the FPGA and AD2 are connected to the computer to provide power and allow us to enter digits into the calculator via the keyboard.

#### 2.2.2 Communicating

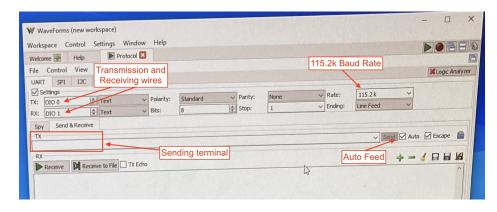

Figure 2: UART Protocol workspace for the Waveforms application. In it you can send data in the sending terminal, set your baud rate, identify transmission and receiving wires, as well as view any receiving signals in the Rx window.

In order to communicate with the calculator, we'll be using the Waveforms app provided by the AD2 to send serial signals to the FPGA. In the protocol workspace, we can send serial data to our system to be processed and displayed on the seven segments displays.

As shown in the figure above it is important to set the baud rate to 115.2k to make sure serial communication is synchronized between the computer and the FPGA.

In the transmission terminal window you can type in inputs to be sent to the AD2 and subsequently the FPGA. In our tests it was helpful to set the feed to auto send such that we wouldn't need to press enter after each input to successfully send it.

#### 2.2.3 Display

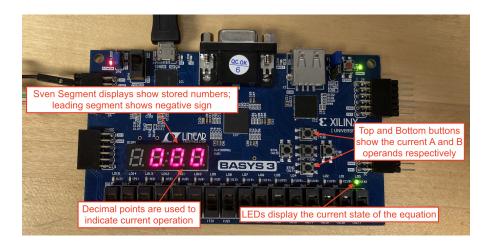

Figure 3: FPGA Display for Calculator. The four seven segment displays show the negative and 3 digits of the inputted and calculated numbers. Decimal points are used to indicate operators (+ - \*/). LEDs in the bottom right corner indicate current state of the equation. Starting with operand A and moving to operator, operand B, and Answer.

When entering data from the keyboard it is important to receive some form of feedback to clarify your entering the correct digits. When using our calculator digits will appear in the seven segment display on the FPGA. Our calculator is reserved to only storing 3 digits so the fourth segment will be used to display the negative sign of the number.

Additionally, valid operators will be displayed as specific decimal points found in the bottom right corner of each segment. Only one decimal point will be lit up at any given time and moving left to right on the FPGA, they represent the division, multiplication, subtraction, and addition.

The LEDs on the bottom right of the board are used to communicate to the user the current state of the equation. In the figure above, the rightmost LED is on, indicating that the user will be inputting the A operand. Moving leftward, the second LED represent entering an operator, the third LED is for the B operand, and the fourth LED is on when an answer is being diplayed.

The last feature we have for the display is the control of the top and bottom buttons of the FPGA to display the currently stored A and B operands. When the top button is pressed, the current display will be overwritten to show the A operand used in the equation. The same goes for the B operand when you press the bottom button.

#### 2.3 Theory of Operation

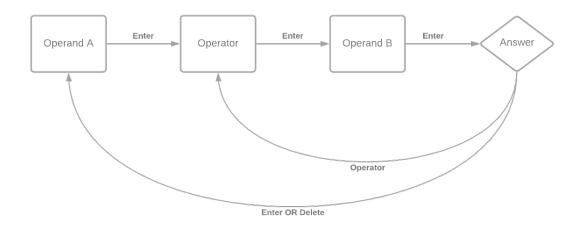

The following steps indicate the typical flow of use for a person using our calculator: (See Figure 11 in Appendix 1.)

Step 1: The user inputs an integer operand between -999 to 999 one digit at a time

- Step 2: The user inputs their desired operation between addition, subtraction, multiplication, and division

- Step 3: The user inputs their second integer operand between -999 to 999, which will enact their desired operation on the previous operand

- Step 4: The user receives an answer to their equation and can either chose to start a new equation(return to step 1) or save this answer and chain it into another equation(move to step 2)

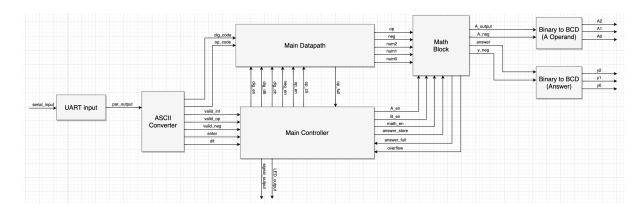

#### 2.3.1 Top Level Design

Before diving into the details of each component, we first figured out what problems we'd come across and describe how our deign plans to overcome them.

Starting to our problem with transmitting to the FPGA, we decided to use UART to process the serial data inputted from our computer and turn it into a single code.

As shown in Figure 5 in Appendix 1, this code would then be fed through an ASCII Converter to interpret the code as one of many keyboard inputs and output the necessary signals. Operators will receive a 2-bit code to differentiate the 4 potential operators; digits will receive there associated 4-bit BCD code; and the negative, enter, and delete keys will all get a single standard logic signal.

Signals sent from the ASCII Converter would then be read by the Controller; which in turn communicates with the Datapath; to organize and store most of this data. The Datapath works to shuttle in digits and operator in from the ASCII Converter and the Controller moderates when, where, and how many signals get stored.

Once all necessary data is collected, the controller will signal the Math Block to preform the calculation. Specifically, the Math Block converts the BCD numbers into signed binary which can then be used to calculate the answer.

Lastly, we decided to use a Binary to BCD converter to take our binary answer (and any other variables) and transform them into a BCD signal readable by the seven segment display. Likewise, other signals outputted by the Controller are given to the seven segment displays to select what should be displayed at each point in the calculation.

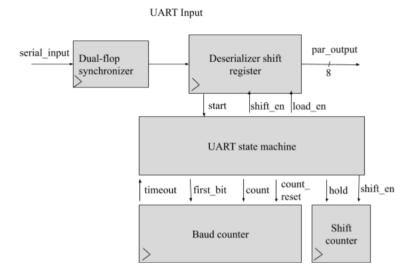

#### 2.3.2 UART

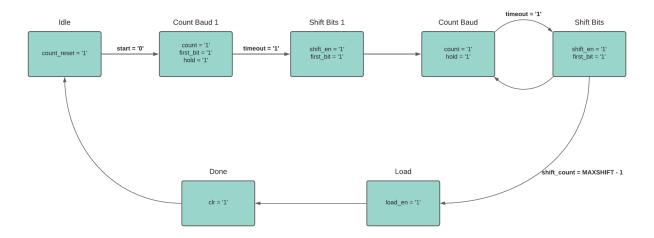

The UART input component takes the serial input from the computer, which arrives at a rate of 115,200 signals per second, and compiles it into an 8-bit parallel signal which can be read by the ASCII converter to determine which value it represents (ASCII codes are 8 bits long). In order to understand how the UART reciever works, it is necessary to understand the components of a UART signal. A UART signal is 10 bits long. The signal is at 1 when it is idle, and the first bit is always 0. This is called the start bit and indicates that the next 8 bits will represent a value. The last bit is always 1, and is called the stop bit. The synchronizer uses two flip-flops to ensure that the incoming signal is being fed to the circuit at the 1MHz system clock speed. This is particularly important because the incoming UART signal is asynchronous. See Figure 6 in Appendix 1 for UART Block Diagram reference. The synchronized signal is passed into the descrializer shift register, which, in conjunction with the UART state machine, converts the serial signal to a parallel signal. The state machine starts in the idle state. See Figure 12 in Appendix 2 for UART State Diagram. When the first bit is detected to be a 0, the state machine moves into the count\_baud\_1 state. This sends a signal to the counter that to start counting. Since the signal comes in at a rate of 115,200 signals per second and the system is at 1MHz, in general, the counter in general counts to 8 before it enables timeout, which, causes the state machine to move to the shift\_1 state, make shift\_en high, and have the contents of the shift register to be shifted. It is ideal to read the incoming signal in the middle of the signal to get a steady value, so the count\_baud\_1 state enables timeout after 1 clock cycle, thus there is a different state for the subsequent counting and shifting states. After each shift, the shift counter increments. While the counter is counting, the shift counter holds its current value. Once there have been 10 shifts, the load state is entered, during which load en is high and the contents of the shift registers are loaded into the parallel output.

See Figure 15 in Appendix 3 for the simulation image.

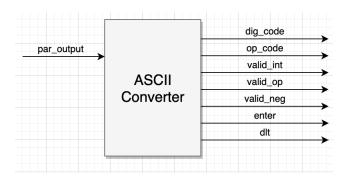

#### 2.3.3 ASCII Converter

The goal of the ASCII converter is to take the 8-bit signal provided by the UART and decode it into specific signals. Knowing that the 8-bit signal (labeled as par\_output in block diagram) represents a single key stroke from a keyboard, we deduced that it would be best to utilize a look-up-table to assign the input number to a specific output signal. (See Figure 7 in Appendix 1 for ASCII Converter Block Diagram).

To do this we first had to decide which keys would be registered to which signals. This was fairly straightforward and by using an ASCII look up table we were able to figure what the par\_output code would be for keys associated with the numbers 0-9, all necessary operators(+ - \* /), and the enter key. Consequently, both the backspace and delete key were not eligible inputs for the Waveform program that we were using to communicate with the system. Instead, we chose to register the spacebar as our primary delete key for the continuation of our project.

The actual hardware implementation of our ASCII Converter was just a look-up-table to check the input signal and set the corresponding output signals. For example; when the par\_output signal is recognized to be some number, valid\_int will go high and dig\_code will parse the input into its BCD counterpart. The same goes for valid\_op and op\_code for when an operator code is detected, valid\_neg for when the '-' key is detected, and entr/dlt for when the enter key or spacebar is detected.

For a more detailed analysis of the ASCII converter's operation please review ASCII Converter testbenches 1 (Figure 16) and 2 (Figure 17 in Appendix 3.

#### 2.3.4 Main Controller

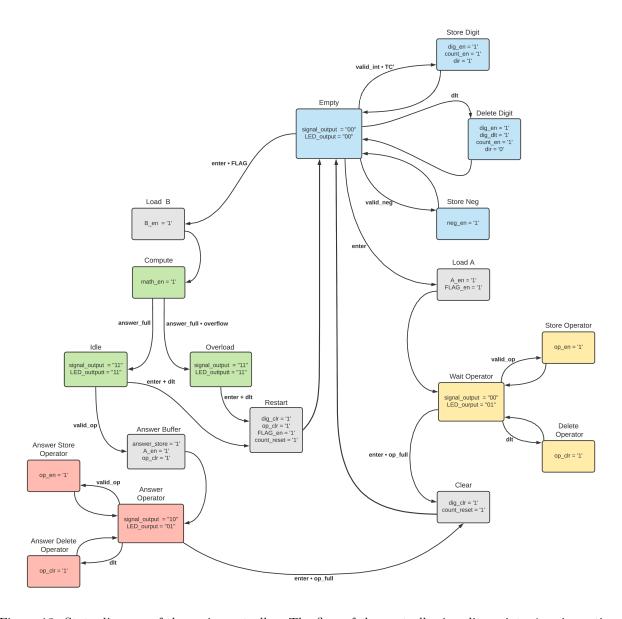

The crux of our calculator is the main controller that signals to many of the other components when to do each of their processes. (See 13 in Appendix 2 for Calculator State Diagram). Once data is decoded by the ASCII Converter it is up to the Controller to read these signals and move though its states, commanding the other components as it goes. The structure of the Controller's state machine is such that we can break down the flow of state into four individual sections (all of which are cycled through using the enter key).

The initial state of the machine begins in the first section that we'll call the "operands" section (colored in blue in the above figure). In this section, user inputs are read to store and delete numbers to form the A and B operands of the equation. Valid integers have the controller signal the datapath to store this number while the spacebar has the controller signal to delete the least significant digit currently stored. Furthermore, the minus symbol in this section is used to toggle the negativity of a number and other operator symbols have no effect on the system. Another feature that is present while in this section is a counter that used to make sure the user does not input more than 3 digits. Our calculator has a capacity to work with numbers between -999 to 999, so it was important to us to keep the user within these bounds during number inputs. Upon leaving this section the controller will signal to take whatever 3-digit number that has been created and store it as the A or B operand as determined by the FLAG signal.

The FLAG signal is used to differentiate A operand from B operand storage. Upon storing a number in operand A, the signal toggles high to signal that the next number stored will be operand B. It is then toggled down when to calculation is complete and the Restart state is reached.

The next section of states is the "operator" section(yellow). Similar to the operands section except user inputs are read to store and delete operators. In this section numbers have no effect and the minus key is registered as a minus symbol. Following this section, the Controller briefly enters the Clear state to make sure all previous digits have been cleared before returning to the Operand section.

After operand A, B, and an operator have been stored the next section the Controller goes to is "computation". This section signals the Math Block to compute an answer and waits to see if the user wishes to chain the answer with another equation or start again from scratch. If the answer generated, overflows the calculator's capacity then the Controller will move to the Overload state which requires the user to begin a new equation. Alternatively, any other numerical answer can be chained into a new equation by entering an operator. This will move the Controller into a brief buffer state to store the answer as the A operand before going to the final section.

The "chain operator" state(Red) is nearly identical to the "operator" section except for the signal\_output signal. This signal(along with LED\_output) communicate with the seven segment display to tell them which numbers to show. In order to show the answer and new operator at the same time, we needed to create this additional section with a separate signal\_output code.

For a waveform clarification on the controller's operation, please see the Calculator Controller Testbench (Figure 18) in the Appendix 3.

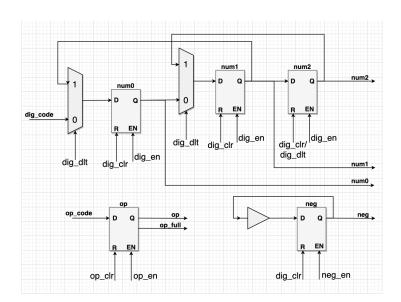

## 2.3.5 Main Datapath

According to the operating instructions of our system, the user will enter in a single digit at a time to ultimately form a 3-digit number between -999 and 999. In order to take single digits and assemble them into full numbers, we needed a way to preserve their order as multiple numbers are entered; this is done in the calculator's Datapath. (See Figure 8 in Appendix 1 for Datapath Block Diagram).

When the dig\_en signal is sent from the Controller, each number register receives the previous registers digit and num0 receives the newest dig\_code from the ASCII converter. Likewise, when dig\_dlt is sent, each number register is enabled to tak in a new digit, but the digit they receive is taken from the register ahead of them.

As you can see in the diagram above the multiplexer determine where the data being stored comes from. Its select bit is the dig\_dlt signal from the Controller; when low it sends the previous register's digit, and when its high it sends the following register. It should also be noted that the num2 register will always be reset when the dig\_dlt or dig\_clr signals are passed to ensure that a zero is passed back to the previous register when the delete signal is sent.

This Datapath also controls the current state of the numbers negativity. Whenever the neg\_en signal is passed to the Datapath, the neg output will toggle between high and low with every press. We can also see in the figure above that the dig\_clr signal also resets the current state of the neg register because negativity is very much tied to the actual number itself.

Lastly, the Datapath stores and outputs the current operator inputted into the system. When op\_en is sent, the op\_code from the ASCII converter is stored in the register and an op\_full signal is sent back to the controller. This signal is to indicate that a operator has been stored and user can officially move on to the next state.

A full waveform of the Datapath's operations can viewed in Appendix 3 under Calculator Datapath Testbench. (Figure 19.)

#### 2.3.6 Math Block

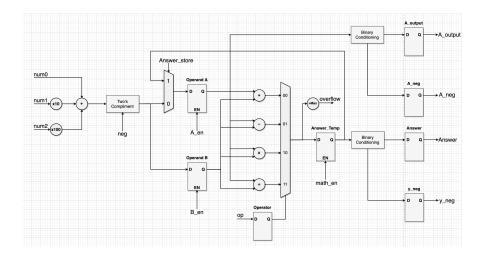

Following up on the calculator's Datapath, the Math Block takes in its digits(num0-2), negative, and operator to form an equation for computation. (See Figure 9 in Appendix 1 for Math Block Diagram).

As a reminder, the num signals from the Datapath represent the 3 digits of a base 10 number. So before computation num0, num1, num2 are turned into a single binary number by multiplying the hundreds digit(num2) by 100, the tens digit(num0) by 10, and adding them all together. Additionally, if a negative is present for this number then the system will preform a two's compliment conversion to make the number a

negative. After this conversion, the new signed binary number is stored in operand A or B (as decided by the controller) until it is needed for computation.

Speaking of which, the computation preformed is determined by the stored operator value also from the datapath. This can be seen as the multiplexer that takes its select bit as the op signal. This value is computed but not stored officially until the math\_en signal is outputted high by the controller.

After an answer is calculated it is stored in the Answer\_temp register and answer\_full signal is fired directly back to the Controller. The new answer is then immediately checked to see if it exceeds the calculators maximum value; if so the overflow signal goes high.

Likewise, after the an answer is generated, it runs through binary conditioning to separate the negative sign from the rest of the number. This is to make the outputting answer digestible for the binary to BCD converter while preserving the negativity of the number. The specific process of the binary conditioning block is as follows: the number is check to see if it less than 0; if so, two's complement is preformed and y\_neg/A\_neg is set high. The same process is applied to the A operand which is also run through its own binary to BCD converter so it can also be shown on the seven segment display.

One last feature of the Math block is its ability to store the computed answer back into the A operand. When the controller sends the Answer\_store signal it'll loop the Answer\_temp signal back to the operand A register for storage. This allows the user to chain answers into new equations following a calculation.

Please refer to Computation Testbench (Figure 20) in Appendix 3 for an in-depth example of operation.

#### 2.3.7 Binary to BCD

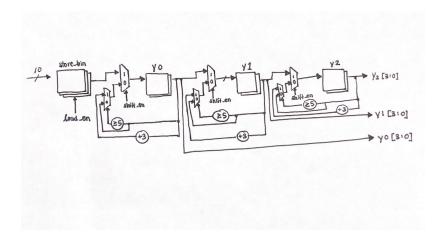

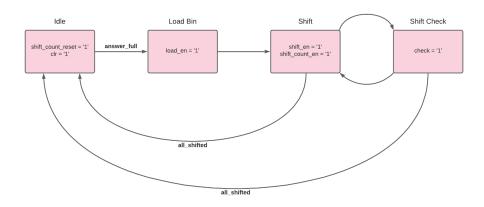

The binary to BCD block is necessary to convert the signed binary number, the calculation form, into sets Binary Coded Decimal bytes, which are sent to the 7-segment display for output. (See Figure 10 in Appendix 1 for Binary to BCD Converter). This is done according to the Double Dabble algorithm. (https://en.wikipedia.org/wiki/Double\_dabble) The binary to BCD converter takes in a 10-bit unsigned value. The output will be three 4-bit numbers that correspond to the three digits of the associated decimal number. (0000 0000 0000, with the first group of four representing the 100s digit and the third group of four representing the 1s digit). The most significant bit of the binary number gets shifted into the least significant bit of the 12 BCD bits. Then the binary number is shifted over so there is a new msb. This occurs 12 times. If at any point a group of 4 has a value greater than or equal to 5, 3 is added to it. This is implemented with multiplexers and a state machine. (Intially loads all the digits in, then shifts and checks if anything is greater than or equal to 5 each time). (See Figure 14 in Appendix 2 for the Binary to BCD State Diagram.) Each time a shift occurs, a shift count is incremented. Once 10 shifts have occurred, the 3 BCD numbers are outputted.

(See Figure 21 in Appendix 3 for the simulation of binary to BCD).

#### 2.3.8 Display

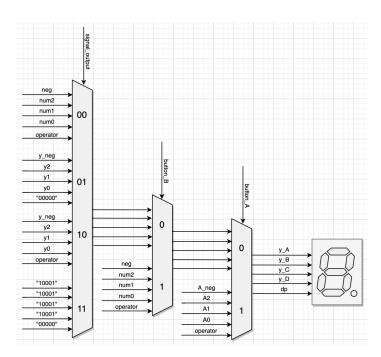

(See Figure 11 in Appendix 1 for Display Block Diagram).

Although we now have all of our desired signals in the form that is transferable to the seven segment display; we'll need some sort of way to select which signal is displayed at any given time. And by focusing on the keyword "select" we immediately understood that we should use a multiplexer to do this job. There are 4 seven segment displays that we have programmed to take a 5-bit input determining there output. Including the decimal point to signify the current operator and we have a total of 5 inputs to shuttle to the seven segments. Furthermore, we have four potential outputs to display at any given time: the digits and operators being inputted by the user, the answer, the answer and the operator the user is inputting(for chaining), and an overload sequence for when the answer is too big.

An RTL design of this block can be seen in the figure above, as you see, the first round of signal selection is conducted by the signal\_output signal from the controller. This clarifies what section of the equation the system is currently in and selects the appropriate output.

Two multiplexers follow this selection, each of which are for the additional button features that allow the user to view each operand of the equation. Signals button\_A and button\_B represent the top and bottom buttons on the FPGA board and when pressed will select the corresponding operand to be displayed on the seven segments. It should also be noted that selection of operand A has priority over operand A as seen in the figure above.

This same sort of selection process is used to determine which LED should light up in the calculator sequence. As you progress through the calculator, the signal LED\_output will count from 1 to 4 indicating if the user needs to input operand A, an operator, operand B, or what to do with the answer.

#### 3 Evaluation

## 3.1 Functionality

The goal of this project was to design and build a functioning calculator using what we've learned form ENGS31. Specifically, we were tasked with creating calculator that could receive external keyboard inputs, preform the basic mathematics operations, and display our answer on seven segment displays. With those criteria (and some we created) we were very much successful in our endeavour.

Our calculator works almost exactly as we planned it to; it takes in numbers from a keyboard and actively displays them on the seven segments. These numbers then form our operands and can be applied to the main mathematical operations with the answer successfully being displayed.

Within the provided time frame for design we were also able to add additional feature to help users and increase functionality. We made it so both positive and negative numbers can be processed. Added LED

sequencing to notify the user their current state within the equation. Allowed the user to check their A and B operands after calculating their answer. Handle potential answer overflow scenarios. And gave the users the option to chain answers into another equation for more options.

#### 3.2 Review

Looking back on the construction of the calculator there were a lot of aspects that were really cool to work on. Figuring out the seven segment displays and being able to control their output using the FPGA buttons was really nice. We originally included this feature as a way to debug our code; such that we could check each intermediate signal to see how out numbers changed as they flowed through the system. Button upon completion we adapted it slightly to offer some useful information for our user. It was also interesting (and a little bit challenging) to get the system to work with both positive and negative numbers. Casting the variables into unsigned, doing the computation, and translating/resizing the back proved to be more of a challenge than we expected but it was ultimately very cool to see working.

One functionality that we failed to implement was the ability to receive serial signals from the FPGA and display them back on the computer monitor. We ran into many issues with converting the signals back into ASCII codes and getting the timing working for the components to work together. In the end we were unfortunately unsuccessful with this plan and were forced to redesign the display location to the seven segments on the FPGA. But even with this setback, it was really amazing to design a project from the ground up and get to use everything I've learned thus far into making it work.

#### 4 Conclusions

The initial goal of our project was to create a calculator with computer numeric input and computer numeric output that could handle addition, subtraction, multiplication, and division of positive and negative numbers for results up to 3 digits. Our final product is a calculator that uses computer input to add, subtract, multiply, and divide positive or negative numbers. The output is displayed instead on the 7-segment display of the FPGA. We added usability features such as LED status lights and buttons to review inputs. Therefore, the functionality of our design was exactly the same as in our proposal. We chose to output our results differently because we found that sending data back to the computer was not working well. Using the FPGA outputs allowed our design to look more like a calculator and to have the added LED and button features. Future groups considering this project should work on testing the hardware/computer connection early, as this is actually somewhat difficult. It also allows them to see what the system is outputting, which is helpful for debugging. Additionally, connecting the 7-segment display for debugging purposes is very useful for monitoring what is happening at every step of the calculation process. Overall, implementing ways to assess what is happening within the design is essential. Wheres with computer coding it is possible to have the computer print values, with digital design, it is necessary and important to implement a hardware equivalent.

## 5 Acknowledgements

In this project Sarah worked on the design and construction of the UART and serial communication of the computer with the calculator. Likewise, she also designed the data conversion between Binary to BCD using the double dabble algorithm. Gavin was tasked with the main controller and datapath of calculator and how it would sort and process inputs from the user. He also designed the Math block and how to chain answers into new equations. Both team members worked together to debug, testbench, and implement every aspect of the program and worked together to design an intuitive display and additive features for the users.

We would also like to thank Ben Dobbins, Professor Eric Hansen, and our TA Yefri for their help and guidance during the constructs of this calculator.

# 6 References

For the binary to BCD conversion process: https://en.wikipedia.org/wiki/Double\_dabble

# Appendix

The Calculator Group 9 - Gavin Burns and Sarah Hutchinson

# Appendix 1: Block Diagrams

System Flow

Figure 4: Example Flow of Use

## System Block Diagram

Figure 5: The top level diagram for our project. Serial data is processed in the UART where it is turned into an 8-bit signal. The ASCII Converter decodes this signal into codes denoting integers, operators, and other valid inputs. These signals are read by the Controller which tells the Datapath to store or delete these values. After two operands and an operator are entered, the Math Block computes the answer. The generated answer is then converted into BCD which will be displayed on the seven segments

## **UART Block Diagram**

Figure 6: UART converter Diagram. Serial input signal goes through a synchronizer and a deserializer and is outputted as an 8-bit par\_output signal, which is sent to the ASCII Converter

#### ASCII Converter Block Diagram

Figure 7: ASCII converter Diagram. 8-bit par\_output signal is fed in and decoded into a variety of signals to be interpreted by the Datapath and Controller

## Datapath Block Diagram

Figure 8: Block diagram of the calculator's datapath. dig\_code and op\_code are taken from the ASCII converter and stored in their respective registers. As multiple digits are input, currently stored digits are shifted through the registers to preserve their order. The reverse process occurs when digits our deleted. A T flip-flop is used to toggle between the numbers negativity as neg\_en is triggered.

#### Math Block Diagram

Figure 9: RTL design of the Math function block. num0, num1, num2, and neg are signals from the Datapath that are converted into a signed binary number and stored in either operand A or B. At the command of the Controller, the math block will compute an answer using the inputted operands and operator; and before outputting the signal, will separate the answer into an unsigned binary number and its negativity. Additionally, operand A can be converted in the same fashion for display on the seven segments and the answer can be stored back into operand A for chaining equations.

Figure 10: Block diagram for Binary to BCD Conversion. 10-bit binary converted to BCD via the Double Dabble Algorithm, which involves shifting the 10-bit binary input into 3 sets of 4 bit numbers (BCD) and adding 3 if the value of a 4 bit group is ever greater than or equal to 5.

### Display Block Diagram

Figure 11: Diagram for the seven segment display output. During the typical process of the calculator, the controller will send signals to the first multiplex to determine what data to display. The user also has the option to press the top and bottom button on the FPGA to display the current A and B operands respectively.

# Appendix 2. State Diagrams

#### **UART State Diagram**

Figure 12: UART State Diagram

#### Calculator State Diagram

Figure 13: State diagram of the main controller. The flow of the controller is split up into 4 main sections with conditioning states in between. Each of the sections in state machine represent holding areas that are waiting on user input to process data and move to the next sections. The blue represents inputting operands, the yellow is inputting operators, the green is from answer computation, and the red is designated for chaining equations together

## Binary to BCD State Diagram

Figure 14: Binary to BCD State Diagram

## Appendix 3: Testbench Waveforms

## **UART** Testbench

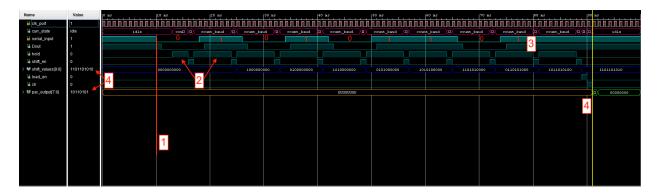

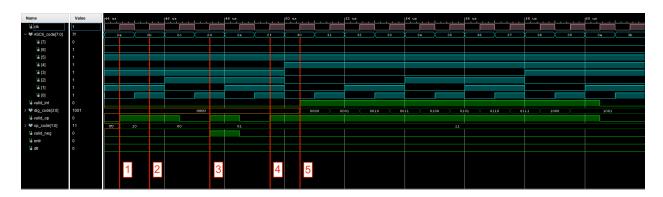

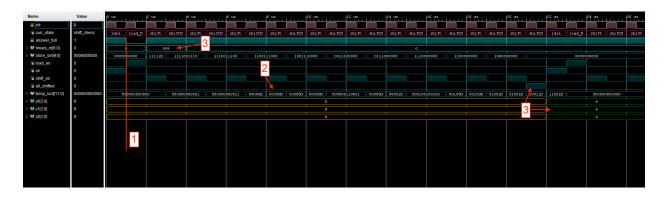

Figure 15: Simulation waveform of our UART converter. Serial signal is delivered in reverse to the UART converter. 1)When the serial input goes low the block is trigger to begin shifting in numbers. 2)In between shifts the values are held constant for the duration of the baud rate. Counter is active for this period and the system is held in the Count\_Baud state. 3)Signal is being fed in reverse order into the UART. 4) When the maximum number of shifts is reached, the shifted values are sent out as a parallel signal. The parallel out signal is taken from the shift\_signal[8 downto 1].

### ASCII Converter Testbench 1

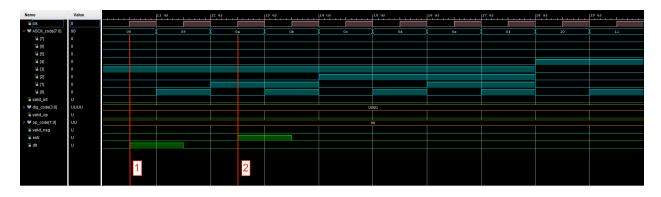

Figure 16: Simulation waveform of the ASCII converter. 1)entr signal goes high when enter key is pressed. 2)dlt(spacebar) signal goes high when delete key is pressed

#### ASCII Converter Testbench 2

Figure 17: Simulation waveform for the ASCII converter. 1)Asterisks key ASCII code is recognized; valid\_op goes high and op code gains the signal for multiplication. 2)Plus key ASCII code; addition stored. 3)Subtraction key ASCII code; subtraction stored and valid\_neg goes high. 4)Slash key ASCII code; division is stored. 5)As digits are recognized, their binary form is stored in dig\_code and valid\_int goes high

#### Calculator Controller Testbench

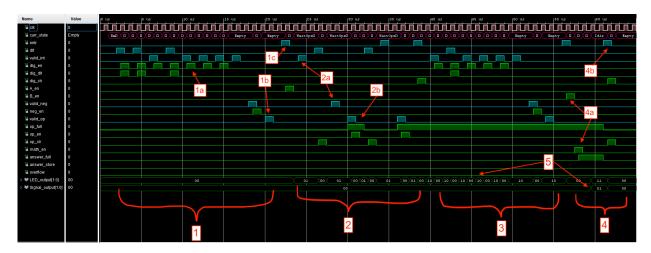

Figure 18: Simulation waveform for the main calculator controller. 1)The "operand A" state; where the user can input any 3 digit integer. 1a)When valid\_dlt and valid\_int signals are detected controller will output dig\_dlt and dig\_en to add/remove stored digits. A max of 3 digits can ever be stored. 1b)Detection of a valid\_op signal has no effect in this state. 1c)Progression to the next state is enacted with the entr signal. 2)The "operator" state. 2a)detecting a valid\_int and valid\_neg signals have no effect in this state. 2b)Detecting a valid\_op will enable op storage and signal that an operator is full. 3)The "operand B" state, same as "operand A" state. 4)Answer state, inputs of previous states our processed and an answer is calculated. 4a)When state is entered math\_en goes high and an answer is generated. 4b)Upon leaving state, all currently stored variables are cleared. 5)As the system progresses through different states, it signals to the seven segment display what should be shown.

## Calculator Datapath Testbench

Figure 19: Simulation waveform of the main calculator datapath. 1)When a dig\_en signal is detected, current dig\_code is stored in the num0 register and currently stored dig\_codes are shifted over in place. 2)dig\_dlt signals will delete the dig\_code stored in num0 and shift other codes back. 3)neg\_en will toggle the negativity of a number. 4)dig\_clr will wipe all number and negativity registers. 5)op\_en and op\_clr store and delete operators respectively. op\_full is only high if an operator is present and op\_clr has not been pressed

#### Computation Testbench

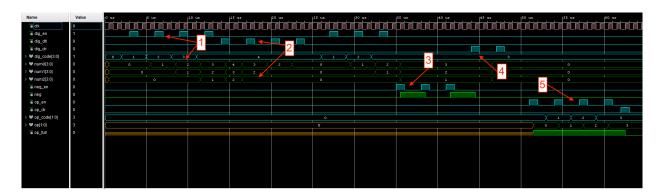

Figure 20: Simulation waveform of computation block; where previous inputs are processed and an answer is output. 1)A\_en and B\_en take the current BCD numbers, compute them into binary and store them in the A and B operands respectively. 2)When math\_en triggers, the system will take the current values of A and B, along with the current operator and calculate and answer. 3)When answer\_store is detected, previous answer is stored in the A operand and can be used for recursion. 4)When an answer exceeds the bounds (-999 to 999) the answer will be set to zero and the overflow signal will go high.

#### Binary to BCD Testbench

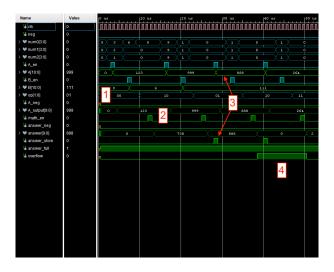

Figure 21: Simulation waveform of the BCD to binary converter. 1)When answer\_full goes high converter begins shifting in binary\_signal. 2)Between each shift the current BCD variables are checked to see if they are greater than 5. If so, the converter adds 3 to them an continues with the shifts. 3)Upon all shifts being conducted each BCD bin is filled with their respective quantity. In this waveform, the number coming in was 999 and the output was a 9, 9, and 9.

## Appendix 4: VHDL Programs

#### UART\_Input Code

```

Company: Thayer School of Engineering

-- Engineer: Gavin Burns & Sarah Hutchinson

-- Create Date: 08/14/2021 12:37:03 AM

-- Design Name:

-- Module Name: ASCII_converter - behavior

-- Project Name: ENGS31 - [REDACTED]

-- Target Devices: Basys3 FPGA

-- Tool Versions:

-- Description:

10

11

12

-- Dependencies:

13

14

-- Revision:

15

Revision 0.01 - File Created

16

-- Additional Comments:

17

18

20

21 library IEEE:

use IEEE.std_logic_1164.all;

22

use ieee.numeric_std.all;

25 entity UART_input is

port(

clk_port: in std_logic; -- 1 MHz serial clock

```

```

serial_input: in std_logic; --inupt from the keyboard

29

par_output: out std_logic_vector(7 downto 0); --output signal

30

par_output_check: out std_logic_vector(7 downto 0)); --for debugging

31

32

33 end UART_input

34 architecture behavior of UART_input is

onstant MAXTIME: integer := 8; -- ~1 MHz /115,200 baud constant MAXSHIFT: integer := 10; --shift 10 times

35

constant MAXTIME:

36

unsigned(13 downto 0) := (others => '0'); --keeps track of time unsigned(4 downto 0) := (others => '0'); --keeps track of number

signal time_count:

37

signal shift_count:

of shifts

std logic vector(9 downto 0) := (others => '0'): --currently

39

signal shift_values:

shifting values

40

std_logic := '0'; --passes the shifting process

std_logic := '0'; --enables shift_values to be shifted

std_logic := '0'; --loads current values into par_out_temp

std_logic := '0'; --clears all currently held values

41

signal hold:

signal shift_en:

42

43

signal load_en:

44

signal clr:

45

std_logic := '0'; --keeps track of time between shifts

signal count:

46

signal timeout: std_logic := '0'; --signals when MAXTIME has been reached signal count_reset: std_logic := '0'; --resets the count

47

48

49

std_logic := '1'; --Synchronizes incoming signal

signal Dsync:

50

std_logic := '1';

signal Dout:

51

signal Start:

std_logic := '1'; --signals the start of the reading

52

53

55

signal

type state_type is (idle, count_baud_1, shift_bits_1, count_baud, shift_bits, load, done

57

--7 state machine

state_type := idle; --begin in Idle

58

signal curr_state:

state_type;

59

signal next_state:

60

62 begin

63

synchronizer: process(clk_port) --syncronizes the incoming signal

64

65

begin

if rising_edge(clk_port) then

66

serial

67

Dsync <=

68

Dout <= Dsync;

end if:

69

end process synchronizer;

70

71

FSM_inc: process(clk_port) --moves through the state machine at the rising edge of the

72

73

if rising_edge(clk_port) then

74

curr_state <= next_state;</pre>

75

end if;

76

77

end process FSM_inc;

78

79

FSM_comb: process(curr_state, timeout, Start, shift_count)

80

begin

81

next_state <= curr_state; --default values</pre>

82

shift_en <= '0';

load_en <= '0';

hold <= '0';

count <= '0';</pre>

83

84

85

86

count_reset <= '0';</pre>

87

first_bit <= '0';</pre>

89

clr <= '0':

90

case curr_state is

91

when idle =>

92

93

count_reset <= '1'; --reset count</pre>

94

if Start = '0' then --if incoming signal goes low

next_state <= count_baud_1; --move to Count_Baud_1(start shifting in</pre>

95

96

bits)

97

end if;

99

when count_baud_1 =>

count <= '1'; --begin counting(for baud rate)

first_bit <= '1';</pre>

100

101

hold <= '1'; --hold onto current value

102

103

if timeout = '1' then --when MAXCOUNT is reached

next_state <= shift_bits_1; --move to Shift_Bits_1</pre>

104

end if;

106

107

when shift_bits_1 => shift_en <= '1';

108

109

--shift in new bit

first_bit <= '1';

next_state <= count_baud; --else move to count Baud

112

```

```

113

114

when count_baud =>

count <= '1'; --begin counting(for baud rate)

hold <= '1'; --hold current values</pre>

117

if timeout = '1' then --when MAXCOUNT is reached

next_state <= shift_bits; --move to Shift_Bits</pre>

119

end if;

120

121

when shift_bits =>

shift_en <= '1'; --shift in new bit</pre>

122

123

124

if shift_count >= (MAXSHIFT-1) then --if shift_count is greater than

MAXSHIFT - 1

next_state <= load; --move to Load state</pre>

126

127

next_state <= count_baud; --else move to count Baud</pre>

128

129

end if:

130

when load =>

131

load_en <= '1'; --load in currently shifted values</pre>

132

133

134

next_state <= done; --move to Done</pre>

135

when done =>

136

clr <= '1'; --clear all currently held values(get ready for next set of values

137

)

138

139

next_state <= idle; --move to Idle</pre>

140

end case;

141

end process FSM_comb;

142

144

\verb|shift_counter: process(clk_port, shift_en, \verb|hold|)| -- counts the number of shifts|

145

begin

if rising_edge(clk_port) then --on rising edge

146

'1' then --if hold is high

147

if hold =

shift_count <= shift_count; --hold values

elsif shift_en = '1' then --if shift_en is high

149

shift_count <= shift_count + 1; --increment shift count</pre>

150

else

shift_count <= (others => '0'); --else, reset count

152

end if;

153

end if:

154

end process;

156

timer: process(clk_port, count_reset, first_bit, time_count, count) --counts for baud rate

157

158

begin

if rising_edge(clk_port) then --on rising edge

160

if count =

^{\prime}1, then --if count is high

time_count <= time_count + 1; --increment time_count

if first_bit = '1' then --if this is the first bit

161

162

if time_count >= (MAXTIME/2 - 3) then --set timeout a little sooner

163

timeout <= '1'

164

time_count <= (others => '0'); --reset count

165

166

else

timeout <= '0':

167

end if:

168

else --if not the first bit

169

if time_count = (MAXTIME - 2) then --timeout triggers at normal rate

timeout <= '1';</pre>

170

171

time_count <= (others => '0');

172

173

else

timeout <= '0';

174

175

end if:

176

177

else

time_count <= time_count; --defualt</pre>

178

end if:

179

180

if count_reset = '1' then --if count_reset is high

time_count <= (others => '0'); --reset time_count

181

182

183

end if;

end if;

184

end process timer;

185

186

RTL: process(clk\_port) --controls the shifting and loading of the bits

187

188

begin

if rising_edge(clk_port) then --on rising edge

189

Oout = '0' then --if Dout gows low

Start <= '0'; --Start mimics

if Dout =

190

191

192

193

Start <= '1'; --else, Start also mimics

194

end if:

195

if shift_en ='1' then --if shift_en is high

196

shift_values <= Dout & shift_values(9 downto 1); --take in new value and right

shift

198

shift_values <= shift_values; --else, hold current value</pre>

199

end if;

200

```

```

202

203

204

205

the values being input)

207

par_out_temp <= par_out_temp; --else, hold current values

end if;</pre>

208

209

211

par_output <= par_out_temp; --at the end of the cycle output the newly loaded</pre>

values

end if;

end process RTL;

212

213

214

215 end behavior;

```

```

_{2} -- Company: Thayer School of Engineering

3 -- Engineer: Gavin Burns & Sarah Hutchinson

5 -- Create Date: 08/16/2021 09:33:50 AM

-- Design Name:

-- Module Name: ASCII_converter - behavior

-- Project Name: ENGS31 - [REDACTED]

-- Target Devices: Basys3 FPGA

10 -- Tool Versions:

11 -- Description:

12

-- Dependencies:

14 --

15 -- Revision:

16 -- Revision 0.01 - File Created

-- Additional Comments:

17

19

20

21

22 library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

^{26} -- Uncomment the following library declaration if instantiating ^{27} -- any Xilinx leaf cells in this code.

27 --

28

--library UNISIM;

--use UNISIM.VComponents.all;

30

{\tt 31} entity ASCII_converter is

Port ( clk: in STD_LOGIC; -- 1 MHz

32

ASCII_code : in STD_LOGIC_VECTOR(7 downto 0); --8bit ASCII code from serial

33

34

op_code : out STD_LOGIC_VECTOR(1 downto 0); --operator code for (+ - * /)

dig_code : out STD_LOGIC_VECTOR(3 downto 0); --digit code for (0-9)

valid_int : out STD_LOGIC; --signal valid integer

valid_op : out STD_LOGIC; --signals valid operator

valid_neg : out STD_LOGIC; --signals negative symbol

35

36

37

38

39

entr : out STD_LOGIC; --signals enter key

dlt : out STD_LOGIC); --signals delete key

42 end ASCII converter:

44 architecture behavior of ASCII_converter is

47

ASCII_converter: process(clk)

48

49

begin

50

if rising_edge(clk) then

51

52

case ASCII_code is

53

when "001000000" => --delete key

dlt <= '1'; --delete code

55

56

when "00001000" => --backspace key

57

dlt <= '1'; --delete code

58

59

when "00001010" => --enter key

60

entr <= '1'; --enter code

61

62

63

when "00101011" => --plus key

64

valid_op <= '1';</pre>

65

op_code <= "00"; --addition code

66

67

when "00101101" => --minus key

68

valid_neg <= '1';

valid_op <= '1';

op_code <= "01"; --subtraction code</pre>

69

70

71

72

when "00101010" => --asterisks key

valid_op <= '1';

op_code <= "10"; --multiplication code</pre>

73

74

75

76

when "001011111" => --slash key

valid_op <= '1';

op_code <= "11"; --division code</pre>

77

79

80

when "00110000" => --0 key

81

valid_int <= '1';</pre>

82

dig_code <= ASCII_code(3 downto 0); --take the last 4 digits</pre>

83

85

when "00110001" => --1 \text{ key}

valid_int <=

86

dig_code <= ASCII_code(3 downto 0); --take the last 4 digits</pre>

87

88

when "00110010" => --2 key

```

```

valid_int <= '1';</pre>

dig_code <= ASCII_code(3 downto 0); --take the last 4 digits</pre>

91

92

when "00110011" => --3 key

93

valid_int <= '1';</pre>

94

95

dig_code <= ASCII_code(3 downto 0); --take the last 4 digits</pre>

96

when "00110100" => --4 key valid_int <= '1';

97

98

dig_code <= ASCII_code(3 downto 0); --take the last 4 digits</pre>

99

100

when "00110101" => --5 key valid_int <= '1';

101

102

dig_code <= ASCII_code(3 downto 0); --take the last 4 digits</pre>

104

when "00110110" => --6 key valid_int <= '1';

105

106

dig_code <= ASCII_code(3 downto 0); --take the last 4 digits</pre>

107

108

when "00110111" => --7 key

109

valid_int <= '1';</pre>

110

dig_code <= ASCII_code(3 downto 0); --take the last 4 digits</pre>

111

112

when "00111000" => --8 key valid_int <= '1';

113

114

dig_code <= ASCII_code(3 downto 0); --take the last 4 digits</pre>

115

116

when "00111001" => --9 key

valid_int <= '1';

dig_code <= ASCII_code(3 downto 0); --take the last 4 digits</pre>

117

118

119

120

n others =>

--op_code <= (others => '0');

--dig_code <= (others => '0');

valid_int <= '0'; --set them all off for all other cases

valid_op <= '0';

valid_neg <= '0';

entr <= '0';

dlt <= '0';</pre>

121

123

124

125

126

128

129

end case;

end if;

130

end process;

131

end behavior;

```

#### Num\_Controller Code

```

_{2} -- Company: Thayer School of Engineering

3 -- Engineer: Gavin Burns & Sarah Hutchinson

5 -- Create Date: 08/11/2021 11:39:17 AM

-- Design Name:

6

-- Module Name: num_controller - behavior

-- Project Name: ENGS31 - [REDACTED]

-- Target Devices: Basys3 FPGA

10 -- Tool Versions:

-- Description:

11

12

13 -- Dependencies:

14 --

15 -- Revision:

16 -- Revision 0.01 - File Created

-- Additional Comments:

17

19 -----

20

21

22 library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

^{26} -- Uncomment the following library declaration if instantiating ^{27} -- ^{\rm any} Xilinx leaf cells in this code.

27 --

--library UNISIM;

28

--use UNISIM. VComponents.all;

30

31 entity num_controller is

generic(

32

NUM_DIGITS: integer:= 3); --control the largest number of digits

33

NUM_DIGITS: integer:= 3); --control the largest number of digits

Port (clk: in STD_LOGIC; --clock signal

valid_int: in STD_LOGIC; --signals valid integer

valid_op: in STD_LOGIC; --signals valid operator

valid_neg: in STD_LOGIC; --signals valid negative symbol

entr: in STD_LOGIC; --signals enter key

dlt: in STD_LOGIC; --signals delete key

op_full: in STD_LOGIC; --signals that an operator has been input

34

35

36

37

38

39

answer_full : in STD_LOGIC; --signals that an answer has been computed overflow : in STD_LOGIC; -- signals that the answer has overflown

41

42

43

dig_en : out STD_LOGIC; --enables digit storage dig_dlt : out STD_LOGIC; --deletes least significant digit dig_clr : out STD_LOGIC; --clears all digit registers op_en : out STD_LOGIC; --enables operator storage op_clr : out STD_LOGIC; --clears operator register neg_en : out STD_LOGIC; --toggles number negativity

44

45

47

48

49

A_en : out STD_LOGIC; --enable storage into the A operand B_en : out STD_LOGIC; --enables storage into the B operand

50

51

math_en : out STD_LOGIC; --enables computation

52

LED_output: out STD_LOGIC_VECTOR(1 downto 0); --determines what is output to the

53

computer

signal_output: out STD_LOGIC_VECTOR(1 downto 0); --determines what is output to

54

the computer

answer_store: out STD_LOGIC); --stores the operand in operand A

55

57 end entity;

architecture behavior of num_controller is

59

type state_type is (Empty, StoreDigit, StoreNeg, DeleteDigit, LoadA, LoadB, WaitOperator

, StoreOperator, DeleteOperator, Clear, Restart, Compute, oops, Idle, AnswerBuffer,

AnswerWaitOperator, AnswerStoreOperator, AnswerDeleteOperator); --13 states

signal curr_state: state_type:= Empty; -- start in EMPTY state

62

63

signal next_state: state_type;

signal count: unsigned(2 downto 0):= (others => '0'); --counts the number of times a

65

digit has been entered (MAX 3)

signal output_temp: std_logic_vector(1 downto 0):= (others => '0');

signal output_temp. std_logic:= '0'; --enables count increment signal count_reset: std_logic:= '0'; --signal to reset counter signal dir: std_logic:= '0'; --determine if count goes up or down signal TC: std_logic:= '0'; --output signal when max is reached

67

69

70

71

signal FLAG_en: std_logic:= '0'; --enable FLAG toggle

72

signal FLAG: std_logic:= '0'; --determines which operand

73

74

75 begin

76

Controller_Update: process(clk)

77

78

if rising_edge(clk) then

curr_state <= next_state; --move to next state at the start of the next clock</pre>

80

cycle

end if;

81

end process;

82

```

```

{\tt Controller\_Logic:\ process(curr\_state,\ valid\_int,\ valid\_op,\ valid\_neg,\ entr,\ dlt,\ op\_full}

answer_full, TC, FLAG, overflow, output_temp)

85

begin

next_state <= curr_state; --default values</pre>

86

dig_en <= '0';

dig_dlt <= '0';

dig_clr <= '0';

op_en <= '0';

87

89

90

op_clr <= '0';

91

neg_en <= '0';

92

A_en <= '0';

B_en <= '0';

math_en <= '0';

93

94

95

answer_store <= '0';</pre>

96

count_en <= '0';

97

count_reset <= '0';

FLAG_en <= '0';

dir <= '0';

99

100

signal_output <= "00";

LED_output <= "00";

101

102

103

case curr_state is

when Empty => --begin in empty

104

signal_output <= "00";

106

107

if(FLAG = '1') then

108

LED_output <= "10";

109

else

LED_output <= "00";

end if;

112

113

114

if ((valid_int AND NOT(TC)) = '1') then --if a number is recognized and the

registers aren't filled

next_state <= StoreDigit; --go to STORE_DIGIT

end if;</pre>

116

117

118

if (valid_neg = '1') then --if a negative symbol is recognized

next_state <= StoreNeg; --go to STORE_NEG</pre>

119

120

121

end if:

122

if (dlt = '1') then --if delete key is recognized

123

next_state <= DeleteDigit; --go to DELETE_DIGIT</pre>

124

end if;

126

if (entr = '1') then --if enter key is recognized

if (FLAG = '1') then --and the flag is raised

127

128

next_state <= LoadB; --go to LOAD_B else --if flag is down

129

130

131

next_state <= LoadA; --go to LOAD_A</pre>

end if;

132

end if:

133

134

135

when StoreDigit => --STORE_DIGIT state

136

dig_en <= '1'; --enable digit storage</pre>

137

138

count_en <= '1'; --enable counter</pre>

139

dir <= '1'; --have it increment +1</pre>

140

141

next_state <= Empty; --return to EMPTY</pre>

142

143

144

when DeleteDigit => --DELETE_DIGIT state

dig_en <= '1'; --enble digit storage

dig_dlt <= '1'; --delete lsd and have the numbers shift back</pre>

145

146

147

148

count_en <= '1'; --enable counter</pre>

149

dir <= '0'; --have it increment -1</pre>

150

151

next_state <= Empty; --return to EMPTY</pre>

154

when StoreNeg => --STORE_NEG state

neg_en <= '1'; --toggle negative sign</pre>

156

157

next_state <= Empty; --return to EMPTY</pre>

158

159

160

when LoadA => --LOAD_A state

161

A_en <= '1'; --load all current digits into operand A

FLAG_en <= '1'; --raise flag; indicates that next operand being stored is B

162

164

next_state <= WaitOperator; --move to WAIT_OPERATOR</pre>

165

166

167

when LoadB => --LOAD_B state

B_en <= '1'; --load all current digits into operand A

next_state <= Compute; --move to COMPUTE; carries out the math operations</pre>

169

170

171

```

```

when WaitOperator => --WAIT_OPERATOR state

signal_output <= "00";

LED_output <= "01";</pre>

174

176

if (valid_op = '1') then --if an operator is recognized

177

next_state <= StoreOperator; --go to STORE_OPERATOR</pre>

end if;

179

180

if (dlt = '1') then --if delete key is recognized

181

next_state <= DeleteOperator; --go to DELETE_OPERATOR</pre>

182

184

if ((entr AND op_full) = '1') then --if enter key is recognized and there is

185

an operator present

next_state <= Clear; --move to CLEAR; clears previous digits and gets

186

ready to store operand {\tt B}

end if;

187

188

189

when StoreOperator => --STORE_OPERATOR state

190

op_en <= '1'; --store the inputed operator

191

192

next_state <= WaitOperator; --retrn to WAIT_OPERATOR; gives user option to</pre>

193

change operator later

194

195

when DeleteOperator => --DELETE_OPERATOR state

op_clr <= '1'; --clear currently stored operator</pre>

196

197

198

next_state <= WaitOperator; --return to WAIT_OPERATOR</pre>

199

200

201

when Clear => --CLEAR state

202

dig_clr <= '1'; --clear all current g=digits and reset negativity</pre>

203

204

count_reset <= '1'; --reset count</pre>

205

206

next_state <= Empty; --move to EMPTY</pre>

207

208

209

when Compute => --COMPUTE state

210

math_en <= '1'; --compute the ansewer

211

212

if (answer_full = '1') then --when an answer is ready

if(overflow = '1') then

213

214

next_state <= oops;</pre>

215

216

else

next_state <= Idle;</pre>

217

219

end if;

220

when oops =>

221

signal_output <= "11";

222

LED_output <= "11";

223

224

if ((entr OR dlt) = '1') then --if enter or delete is recognized

next_state <= Restart; --restart the entire process; begining with</pre>

225

226

operand A

227

228

when Idle =>

signal_output <= "01";

LED_output <= "11";</pre>

229

230

231

232

if (valid_op = '1') then --if operator recgnized

233

next_state <= AnswerBuffer; --move to STORE_OPERATOR; skips A operand</pre>

since the answer is stored in there

235

end if:

236

if ((entr OR dlt) = '1') then --if enter or delete is recognized

237

next_state <= Restart; --restart the entire process; begining with</pre>

238

operand A

239

end if:

240

when AnswerBuffer =>

241

answer_store <= '1'; --enable storage of the answer

242

A_en <= '1'; --store the answer in operand A; this lets the user connect

equations together

op_clr <= '1'; --clear currently stored operator</pre>

244

245

next_state <= AnswerStoreOperator;</pre>

246

when AnswerWaitOperator => --WAIT_OPERATOR state

248

signal_output <= "10";

LED_output <= "01";</pre>

249

250

251

if (valid_op = '1') then --if an operator is recognized

252

253

next_state <= AnswerStoreOperator; --go to STORE_OPERATOR</pre>

254

end if;

255

if (dlt = '1') then --if delete key is recognized

256

```

```

next_state <= AnswerDeleteOperator; --go to DELETE_OPERATOR</pre>

257

258

259

if ((entr AND op_full) = '1') then --if enter key is recognized and there is

260

an operator present

next_state <= Clear; --move to CLEAR; clears previous digits and gets

ready to store operand B

262

end if:

263

264

when AnswerStoreOperator => --STORE_OPERATOR state

265

266

op_en <= '1'; --store the inputed operator

267

next_state <= AnswerWaitOperator; --retrn to WAIT_OPERATOR; gives user</pre>

268

option to change operator later

270

when AnswerDeleteOperator => --DELETE_OPERATOR state

271

op_clr <= '1'; --clear currently stored operator

272

273

274

next_state <= AnswerWaitOperator; --return to WAIT_OPERATOR</pre>

276

when Restart => --RESTART state

dig_clr <= '1'; --clear currently stored digits

op_clr <= '1'; --clear operator

FLAG_en <= '1'; --lower flag; returning to A operand storage</pre>

277

278

279

280

281

count_reset <= '1'; --reset count</pre>

282

next_state <= Empty; --move to EMPTY</pre>

283

end case;

284

end process;

285

286

287

Counter: process(clk, count) --controls the user from pushing out the msd

288

if rising_edge(clk) then

289

if(count_reset = '1') then --if reset count is enabled; priority over count

290

enable

count <= (others => '0'); --reset count

elsif(count_en = '1') then --else if count is enabled

if(dir = '0' AND NOT(count = 0)) then --and direction is low and count isnt

291

292

293

already at 0

294

296

end if;

297

end if;

298

end if;

299

300

TC <= '0'; --default value if(count >= NUM_DIGITS) then --if count is higher or equal to than the number of

301

302

permitted digits (3)

TC <= '1'; --TC goes high

end if;

304

305

end process;

306

FlagPole: process(clk) --toggles the current state of the FLAG indicator

307

308

begin

if rising_edge(clk) then

if (FLAG_en = '1') then

FLAG <= NOT(FLAG); --toggle FLAG</pre>

310

311

end if;

312

end if;

313

end process;

314

315 end behavior;

```

#### Num\_Datapath Code

```

_{2} -- Company: Thayer School of Engineering

3 -- Engineer: Gavin Burns & Sarah Hutchinson

5 -- Create Date: 08/11/2021 08:13:33 PM

-- Design Name:

6

-- Module Name: ASCII_converter_tb - testbench

-- Project Name: ENGS31 - [REDACTED]

-- Target Devices: Basys3 FPGA

10 -- Tool Versions:

-- Description:

11

12

-- Dependencies:

14 --

15 -- Revision:

16 -- Revision 0.01 - File Created

-- Additional Comments:

17

19

20

21 library IEEE:

use IEEE.std_logic_1164.all;

24 entity num_datapath is

--generic(

25

--NUM_DIGITS: integer); --control the largest number of digits

26

port(

27

clk:in std_logic; --clock signal

28

dig_code: in std_logic_vector(3 downto 0); --BCD number between 0-9

op_code: in std_logic_vector(1 downto 0); --operator code: 00=addition, 01=sub, 10=

29

30

mult, 11=div

dig_en: in std_logic; --enables digit storage

dig_dlt: in std_logic; --deletes least significant digit

dig_clr: in std_logic; --clears all digit registers

31

32

33

op_en: in std_logic; --enable operator storage

op_clr: in std_logic; --clears operator register

neg_en: in std_logic; --toggles number negativity

35

36

37

op: out std_logic_vector(1 downto 0); --entered operator num0: out std_logic_vector(3 downto 0); --one's place num1: out std_logic_vector(3 downto 0); --ten's place num2: out std_logic_vector(3 downto 0); --hundred's place neg: out std_logic; --current negativity

38

39

40

41

42

op_full: out std_logic); --whether an operator is present

43

45 end num_datapath;

46

47 architecture behavior of num_datapath is

48

signal temp_neg: std_logic:= '0'; --for T Flip-Flop

49

signal dig0, dig1, dig2: std_logic_vector(3 downto 0):= (others => '0'); --tmeporary

digits

signal num0_temp, num1_temp, num2_temp: std_logic_vector(3 downto 0):= (others => '0')

51

52

begin

53

operator: process(clk)

54

55

begin

if rising_edge(clk) then --on the rising edge

56

if(op_en = '1') then

op <= op_code; --store operator</pre>

57

58

59

op_full <= '1'; --set operator to full (lets you move to next state

60

end if:

61

if(op_clr = '1') then

62

-op <= others => '0'; --clear operator (default to addition)

op_full <= '0'; --set operator to empty (cannot move on until operator is

63

64

input)

end if;

end if;

65

66

end process;

67

68

negative: process(clk, temp_neg)

69

70

begin

if rising_edge(clk) then --on rising edge

71

if (neg_en = '1') then

72

temp_neg <= NOT(temp_neg); --toggle negativity</pre>

73

75

if(dig_clr = '1') then

temp_neg <= '0'; --reset negativity</pre>

76

77

end if;

78

79

81

neg <= temp_neg; --output current negativity</pre>

82

end process;

83

number: process (clk, dig0, dig1, dig2)

84

begin

```

```

if rising_edge(clk) then -- on rissing edge

if(dig_en = '1') then

dig0 <= dig_code; --shift msd and store entered digit

dig1 <= dig0;

dig2 <= dig1;</pre>

87

88

89

90

91

end if;

92

if(dig_dlt = '1') then

dig0 <= dig1; --delete lsd and shift

dig1 <= dig2;

dig2 <= (others => '0');

93

94

95

end if;

97

98

if(dig_clr = '1') then

dig0 <= (others => '0'); --clear all digits

dig1 <= (others => '0');

dig2 <= (others => '0');

99

100

101

102

end if;

103

104

105

106 --

107 --

108 --

num0_temp <= num0_temp;

num1_temp <= num1_temp;

num2_temp <= num2_temp;</pre>

109

--if(busy_convert = '0') then

num0 <= dig0; --output current digits

num1 <= dig1;

num2 <= dig2;

110

112

113

--end if;

114

115

num0 <= num0_temp;

num1 <= num1_temp;

num2 <= num2_temp;</pre>

116 --

117 --

118 --

end if;

119

120

end process;

121

122

end behavior;

```

#### Math Code

```

-- Company: Thayer School of Engineering

3 -- Engineer: Gavin Burns & Sarah Hutchinson

-- Create Date: 08/16/2021 11:43:22 AM

5

-- Design Name:

6

-- Module Name: Math - Behavioral

-- Project Name: ENGS31 - Operation_[REDACTED]

-- Target Devices: Basys3 FPGA

10 -- Tool Versions:

-- Description:

11

12

-- Dependencies:

14 --

15 -- Revision:

16 -- Revision 0.01 - File Created

-- Additional Comments:

17

19 -----

20

21

22 library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

^{26} -- Uncomment the following library declaration if instantiating ^{27} -- ^{\rm any} Xilinx leaf cells in this code.

27 --

28

--library UNISIM;

--use UNISIM. VComponents.all;

30

31 entity Math is

Port (clk: in STD_LOGIC; --clock signal

32

num0: in std_logic_vector(3 downto 0); --one's place

33

num1: in std_logic_vector(3 downto 0); --ten's place

num2: in std_logic_vector(3 downto 0); --hundred's place

34

35

neg: in std_logic; --current negativity

op: in STD_LOGIC_VECTOR(1 downto 0); --operator

36

37

A_en : in STD_LOGIC; --enables storage of number into A operand B_en : in STD_LOGIC; --enables storage of number into B operand

38

39

{\tt math\_en} : in STD_LOGIC; --enables computation of A and B by op

answer_store : in STD_LOGIC; --stores the answer in the A operand

41

42

answer : out STD_LOGIC_VECTOR(9 downto 0); --outputted answer

43

A_output : out STD_LOGIC_VECTOR(9 downto 0);

44

A_neg : out STD_LOGIC;

overflow: out STD_LOGIC; --signals that the value is beyond -999 or 999 y_neg : out STD_LOGIC; --whether answer is negative our not answer_full : out STD_LOGIC); --signals that an answer is ready to be presented

47

48

end Math;

50

architecture behavior of Math is

52

signal A: SIGNED(10 downto 0):= (others => '0'); --Operand A; 11 bits to store numbers

53

between -999 to 999

signal B: SIGNED(10 downto 0):= (others => '0'); --Operand A; 11 bits to store numbers

54

between -999 to 999

signal answer_temp: SIGNED(20 downto 0):= (others => '0'); --answer; 21 bits to store

numbers between -998001 to 998001

--signal num0_temp: UNSIGNED(10 downto 0):= (others => '0');

--signal num1_temp: UNSIGNED(10 downto 0):= (others => '0');

56

57

--signal num2_temp: UNSIGNED(10 downto 0):= (others => '0');

58

--signal num3_temp: UNSIGNED(10 downto 0):= (others => '0');

constant I: unsigned(6 downto 0):= "1100100"; --needed for BCD conversion

59

60

61

62 begin

63

64

Store: process(clk)

65

begin

if rising_edge(clk) then

66

67

--num0_temp(3 downto 0) <= unsigned(num0);

68

--num1_temp <= resize(10*unsigned(num1), num1_temp'length);

--num2_temp <= resize(I*unsigned(num2), num2_temp'length);

69

70

--num3_temp <= resize(10*unsigned(num2_temp), num3_temp'length);

71

72

if (A_en = '1') then

73

if (answer_store = '1') then

74

A <= answer_temp(10 downto 0); --store the answer into operand A(for

recursion)

76

if(neg = '1') then --if value is negative

A <= NOT(signed(resize(I*unsigned(num2) + 10*unsigned(num1) +</pre>

77

78

unsigned(num0), A'length))) + 1; --two's compliment of the digits

A <= signed(resize(I*unsigned(num2) + 10*unsigned(num1) + unsigned(num0), A'length)); --store digits in operand A

80

end if;

81

end if;

82

elsif (B_en = '1') then

```

```

85

86

B <= signed(resize(I*unsigned(num2) + 10*unsigned(num1) + unsigned(

87

num0), B'length)); --store digits into operand B

88

end if;

end if:

89

90

if(A < 0) then</pre>

91

A_neg <= '1'; --separate the negative

92

93

A_output <= std_logic_vector((NOT(A(9 downto 0)) + 1)); --store the

value in answer

94

A_neg <= '0';

95

A_output <= std_logic_vector(A(9 downto 0)); --store the value of answer

96

97

end if;

98

end if:

end process;

99

100

101

Computation: process(clk, answer_temp)

102

if rising_edge(clk) then

104

105

answer_full <= '0';</pre>

106

107

if (math_en = '1') then

108

109

--answer_temp <= answer_temp;

case op is

when "00" => --addition operator

113

114

answer_temp <= resize(A + B, answer_temp'length); --add A and B</pre>

when "01" => --subtraction operator

116

answer_temp <= resize(A - B, answer_temp'length); --subtract B from</pre>

117

118

when "10" => --multiplication operator

answer_temp <= resize(A * B, answer_temp'length); --multiply A and B</pre>

119

120

121

when "11" => --division operator

answer_temp <= resize(A / B, answer_temp'length); --divide A by B</pre>

123

125

when others =>

answer_temp <= (others => '0'); --set to zero so we can easily see

126

there's an error

end case;

128

129

end if:

130

if(answer_temp > 999 OR answer_temp < -999) then --if the answer is out of

131

answer \leftarrow (others => '0'); --store the value "1000000000" (indicates an

132

overvalued answer)

overflow <= '1'; --signal overflow(this value cannot be stored in A) answer_full <= '1'; --signal that an answer has been generated

133

134

135

if(answer_temp < 0) then</pre>

136

y_neg <= '1'; --separate the negative

answer <= std_logic_vector((NOT(answer_temp(9 downto 0)) + 1)); --</pre>

137

y_neg <=

138

store the value in answer

139

else

140

y_neg <= '0';

answer <= std_logic_vector(answer_temp(9 downto 0)); --store the

141

value of answer

142

end if:

overflow <= '0';

answer_full <= '1'; --signal that an answer has been generated

143

144

end if;

145

146

147

end if:

end process;

148

end behavior;

```

#### Binary to BCD Code

```

_{2} -- Company: Thayer School of Engineering

3 -- Engineer: Gavin Burns & Sarah Hutchinson

5 -- Create Date: 08/17/2021 10:14:52 PM

-- Design Name:

6

-- Module Name: ASCII_converter - behavior

8 -- Project Name: ENGS31 - [REDACTED]

-- Target Devices: Basys3 FPGA

10 -- Tool Versions:

11 -- Description:

12

-- Dependencies:

14 --

15 -- Revision:

16 -- Revision 0.01 - File Created

-- Additional Comments:

17

19

20

21

22 library IEEE;

use IEEE.std_logic_1164.all;

use ieee.numeric_std.all;

26 entity binary_BCD is

port( clk:

in std_logic; --clock signal

27

r_full: in std_logic; --signals that an answer has been generated binary_in: in std_logic_vector(9 downto 0); --binary answer

answer_full:

28

out std_logic_vector(3 downto 0); --BCD number (0-9) lsd

out std_logic_vector(3 downto 0); --BCD number (0-9) mid digit

y2:    out std_logic_vector(3 downto 0)); --BCD

30

31

y0:

32

y1:

out std_logic_vector(3 downto 0)); --BCD number (0-9) msd

33

34

35 end binary_BCD;

36

37 architecture behavior of binary_BCD is

constant NSHIFT:

integer := 10; --number of total shifts

38

unsigned(9 downto 0) := (others => '0');

unsigned(11 downto 0) := (others => '0');

signal store_bin:

39

signal temp_bcd:

std_logic := '0'; --enables shift_cout to increment

std_logic := '0'; --resets shift count

signal shift_count_en:

41

signal shift_count_reset:

42

unsigned(5 downto 0) := "000000"; --counts the number of

signal shift_count:

43

shifts

signal load_en:

std_logic := `0'; --loads the answer into the store_bin

std_logic := '0'; --clears store bin

std_logic := '0'; --right shifts the store_bin into the