AP Applied Physics Letters

Inversion-type indium phosphide metal-oxide-semiconductor field-effect transistors with equivalent oxide thickness of 12 Å using stacked Hf Al O x  $\,$  Hf O 2 gate dielectric

Han Zhao, Davood Shahrjerdi, Feng Zhu, Hyoung-Sub Kim, Injo OK, Manghong Zhang, Jung Hwan Yum, Sanjay K. Banerjee, and Jack C. Lee

Citation: Applied Physics Letters **92**, 253506 (2008); doi: 10.1063/1.2943186 View online: http://dx.doi.org/10.1063/1.2943186 View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/92/25?ver=pdfcov Published by the AIP Publishing

Articles you may be interested in Excellent electrical properties of Ti O 2 Hf Si O Si O 2 layered higher- k gate dielectrics with sub- 1 nm equivalent oxide thickness Appl. Phys. Lett. **92**, 212902 (2008); 10.1063/1.2929680

Inversion-type enhancement-mode Hf O 2 -based GaAs metal-oxide-semiconductor field effect transistors with a thin Ge layer Appl. Phys. Lett. **92**, 032907 (2008); 10.1063/1.2838294

Dielectric relaxation of atomic-layer-deposited Hf O 2 thin films from 1 kHz to 5 GHz Appl. Phys. Lett. **87**, 012901 (2005); 10.1063/1.1988982

Exchange bias and vertical loop shifts in a Co ( 32 Å ) Ni O ( 10 Å ) [ Co ( 4 Å ) Pt ( 6 Å ) ] 4 multilayer Appl. Phys. Lett. **85**, 4971 (2004); 10.1063/1.1814817

Synthesis of 4 Å single-walled carbon nanotubes in catalytic Si-substituted Al P O 4 5 molecular sieves Appl. Phys. Lett. **85**, 1253 (2004); 10.1063/1.1781740

## AP Journal of Applied Physics

*Journal of Applied Physics* is pleased to announce André Anders as its new Editor-in-Chief

## Inversion-type indium phosphide metal-oxide-semiconductor field-effect transistors with equivalent oxide thickness of 12 Å using stacked HfAIO<sub>x</sub>/HfO<sub>2</sub> gate dielectric

Han Zhao,<sup>a)</sup> Davood Shahrjerdi, Feng Zhu, Hyoung-Sub Kim, Injo OK, Manghong Zhang, Jung Hwan Yum, Sanjay K. Banerjee, and Jack C. Lee Microelectronics Research Center, Department of Electrical and Computer Engineering, The University of Texas at Austin, Texas 78758, USA

(Received 18 April 2008; accepted 20 May 2008; published online 25 June 2008)

We present InP metal-oxide-semiconductor capacitors (MOSCAPs) and metal-oxide-semiconductor field-effect transistors (MOSFETs) with stacked HfAlO<sub>x</sub>/HfO<sub>2</sub> gate dielectric deposited by atomic layer deposition. Compared with single HfO<sub>2</sub>, the use of stacked HfAlO<sub>x</sub>/HfO<sub>2</sub> results in better interface quality with InP substrate, as illustrated by smaller frequency dispersion and lower leakage current density. The equivalent oxide thickness of MOSCAPs with 10 Å HfAlO, /25 Å HfO<sub>2</sub> stacked gate dielectric is 12 Å. The MOSFETs with this gate dielectric achieve two times higher transconductance than those with single 35 Å HfO2. They also exhibit drive current of 60 mA/mm and subthreshold swing of 83 mV/decade for 5 µm gate length. © 2008 American Institute of Physics. [DOI: 10.1063/1.2943186]

Recently, III-V compound semiconductors have received a great deal of attention for metal-oxide-semiconductor fieldeffect transistors (MOSFETs) applications due to their higher electron mobility and breakdown field compared to silicon. Among the III-V MOSFETs, inversion-type MOSFETs are preferred over depletion type because of their superior immunity to drain induced barrier lowing effect and punch through leakage and breakdown. Some progress has been made on inversion-type III-V MOSFETs including GaAs MOSFETs with Si or Ge passivation layer and HfO<sub>2</sub> dielectrics,<sup>1,2</sup> or with molecular beam epitaxy (MBE)  $Ga_2O_3$ (Gd<sub>2</sub>O<sub>3</sub>) dielectrics,<sup>3,4</sup> InGaAs MOSFETs with atomic layer deposited (ALD)  $Al_2O_3$  or HfO<sub>2</sub> dielectrics,<sup>5–7</sup> or with Si passivation layer and HfO<sub>2</sub> dielectrics,<sup>8</sup> or with MBE Ga<sub>2</sub>O<sub>3</sub>(Gd<sub>2</sub>O<sub>3</sub>) dielectrics,<sup>9</sup> and InP MOSFETs with ALD  $Al_2O_3$  or  $HfO_2$  dielectrics.<sup>10,11</sup> GaAs inversion-type MOSFETs usually have problems of low drive current.<sup>2,3</sup> While InGaAs MOSFETs can provide large drive current,<sup>6,7</sup> they also exhibit fairly high off-current density and large subthreshold swing [e.g., 240 mV/decade (Ref. 6), 330 mV/decade (Ref. 7)]. On the other hand, InP inversiontype MOSFETs with ALD Al<sub>2</sub>O<sub>3</sub> have shown the capability of high drive current density,<sup>10</sup> and they can provide much smaller off-current density due to larger bandgap (1.34 eV) compared to InGaAs (0.74 eV for In<sub>0.53</sub>Ga<sub>0.47</sub>As). These characteristics make InP a promising alternative material which should be studied for future low-power logic applications.

For Si-based technology, HfO<sub>2</sub> has been widely studied as an alternative gate oxide material to attain further scaling down.<sup>13,14</sup> In addition, there have been some attempts to adopt HfO<sub>2</sub> on III-V semiconductor compounds.<sup>1,2,6,11</sup> However, very little work has been performed on gate oxide scaling down below equivalent oxide thickness (EOT) of 20 Å on III-V MOSFETs. The ALD provides an ex situ technique with which a high quality, thermodynamically stable oxide can be directly placed on III-V substrate,<sup>6,10,15</sup> and favors the scaling of gate oxides. While ALD  $Al_2O_3$  with  $\kappa$  value of 8-10 shows good compatibility with III-V substrate, ALD HfO<sub>2</sub> with  $\kappa$  value of more than 20, which is of course more promising for scaling of gate oxide, always has higher interface state density than ALD Al<sub>2</sub>O<sub>3</sub> with III-V materials.<sup>6,11,16</sup> In this paper, a thin layer of  $HfAlO_x$  nanolaminates was used between HfO<sub>2</sub> and InP to reduce the interface state density, the capacitance-voltage (C-V) and current-voltage (I-V) characteristics of MOS capacitors (MOSCAPs) were investigated and the well-behaved MOSFETs with EOT of 12 Å were realized.

The MOSCAPs were fabricated on n-type InP (100) wafer doped with sulfur  $(5 \times 10^{17} / \text{cm}^3)$ . The surface oxides were removed with the 1% HF solution, followed by 20%  $(NH_4)_2S_x$  dip.<sup>17</sup> For sample (a), 35 Å HfO<sub>2</sub> was deposited by ALD at 200 °C using tetrakis(dimethyl-amino) hafnium  $[Hf(NMe_2)_4]$  and  $H_2O$  as the precursors. For sample (b), HfAlO<sub>x</sub> nanolaminates were used as gate dielectric. The nanolaminates structure consisted of one cycle of hafnium oxide growth and one cycle of aluminum oxide growth (trimethylaluminum and H<sub>2</sub>O as the precursors). This stack was repeated for 15 times to form 30 Å HfAlO<sub>x</sub> at 200 °C. For sample (c), 6 Å HfAlO<sub>x</sub> was deposited at the bottom followed by 25 Å HfO<sub>2</sub> on the top. For sample (d), 10 Å HfAlO<sub>x</sub> was deposited followed by 25 Å HfO<sub>2</sub>. Physical vapor deposited (PVD) TaN was used for gate electrode and e-beam evaporated AuGe/Ni/Au alloy for the backside contact. The n-channel MOSFETs were fabricated on semiinsulating (SI)-InP (100) substrate with a ring-type structure<sup>1</sup> by gate-last process. The surface treatment was performed on SI-InP same as MOSCAPs, then 100 Å Al<sub>2</sub>O<sub>3</sub> (dummy gate oxides) was deposited by ALD at 250 °C. After 35 keV, 5  $\times 10^{14}$ /cm<sup>2</sup> Si ion implantation at the source and drain regions, samples were annealed at 750 °C for 15 s. The Al<sub>2</sub>O<sub>3</sub> layer was then removed by buffered oxide etchant (BOE). After the same surface treatment on these InP samples, 35 Å HfO<sub>2</sub> [sample (a)], or 6 Å HfAlO<sub>x</sub>/25 Å HfO<sub>2</sub> stacked dielectric [sample (c)], or 10 Å HfAlO<sub>x</sub>/25 Å HfO<sub>2</sub> stacked

0003-6951/2008/92(25)/253506/3/\$23.00

<sup>&</sup>lt;sup>a)</sup>Electronic mail: zhaohan@mail.utexas.edu.

use of AIP content is subject to the terms at: http://scitation.aip.org/termsconditions. Downloade 92, 253506-1 © 2008 American Institute of Physics 216.165.95.70 On: Tue, 25 Aug 2014 19:46:44

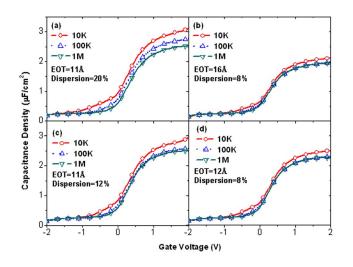

FIG. 1. (Color online) Typical *C-V* characteristics from 10 KHz to 1 MHz for InP MOSCAPs with different gate dielectrics: (a) 35 Å HfO<sub>2</sub> [sample (a)], (b) 30 Å HfAlO<sub>x</sub> [sample (b)], (c) stacked 6 Å HfAlO<sub>x</sub>/25 Å HfO<sub>2</sub> [sample (c)], (d) Stacked 10 Å HfAlO<sub>x</sub>/25 Å HfO<sub>2</sub> [sample (d)]. Frequency dispersion was calculated between 1 MHz and 10 KHz at a gate voltage of 1.5 V.

dielectric [sample (d)] was deposited on separate samples. The TaN gate electrode was deposited by PVD and AuGe/Ni/Au by e-beam evaporation for source and drain Ohmic contact.

Figures 1(a)-1(d) illustrate the typical C-V characteristics of InP MOSCAP for samples (a)–(d), respectively. The EOT was calculated with consideration to the quantum mechanism.<sup>18</sup> Single HfO<sub>2</sub> dielectric on InP [Fig. 1(a)] shows a frequency dispersion as large as 20% from 1 MHz to 10 KHz, while the  $HfAlO_x$  nanolaminates have much better interface with InP, illustrated by a much smaller frequency dispersion of 8% [Fig. 1(b)]. The  $\kappa$  value of the nanolaminates is about 12, calculated from EOT of HfAlO<sub>x</sub> with different physical thicknesses (data not shown). This value is still not high enough for further scaling down. Thus a thin  $HfAlO_r$  at the bottom and another  $HfO_2$  layer on the top were used to obtain a small EOT while maintaining good interface at the same time. C-V of MOSCAPs using 6 or 10 Å HfAlO<sub>x</sub> at the bottom and 25 Å HfO<sub>2</sub> on the top are shown in Figs. 1(c) and 1(d). It has been found that frequency dispersion is reduced with thicker HfAlO<sub>x</sub>, achieving the same amount as the single  $HfAlO_x$  gate dielectric (8%)

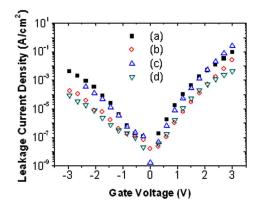

FIG. 2. (Color online) Gate leakage current density  $(J_g)$  versus gate voltage of InP MOSCAPs with different gate dielectrics for sample (a) to sample (d).

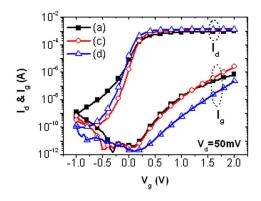

FIG. 3. (Color online) Log-scale drive current  $I_d$  and gate leakage current  $I_g$  versus gate voltage  $V_g$  at  $V_d$ =50 mV for InP MOSFETs with 35 Å HfO<sub>2</sub> (a), or 6 Å HfAlO<sub>x</sub>/25 Å HfO<sub>2</sub> (c), or 10 Å HfAlO<sub>x</sub>/25 Å HfO<sub>2</sub> (d) as gate dielectric (*W*/*L*=600 $\mu$ m/5  $\mu$ m).

when HfAlO<sub>x</sub> is 10 Å thick. The EOT of this gate stack structure is 12 Å, which is close to that of 35 Å single HfO<sub>2</sub> dielectric. The *C*-*V* hysteresis of samples (a)–(d) are 340, 230, 270, and 280 mV, respectively, measured from –2 to 2 V, and the flatband voltage is about 0.31 V for all four kinds of samples. The leakage current density versus gate voltage of sample (a)–(d) is shown in Fig. 2, the leakage current density of 30 Å HfAlO<sub>x</sub> or 10 Å HfAlO<sub>x</sub>/25 Å HfO<sub>2</sub> as the gate dielectric is similar, which is about 2 × 10<sup>-5</sup> A/cm<sup>2</sup> at  $V_g = V_{fb} + 1$  V. This value is one order lower than the leakage current density of 35 Å HfO<sub>2</sub> or 6 Å HfAlO<sub>x</sub>/25 Å HfO<sub>2</sub>.

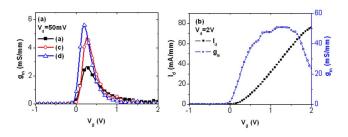

We compared the characteristics of MOSFETs with the same gate dielectrics as MOSCAPs sample (a), (c), and (d) in Figs. 3–5, which have similar EOT of 11–12 Å (Fig. 1). Figure 3 shows the log-scale driver current  $(I_d)$  and gate leakage current  $(I_g)$  versus gate voltage  $(V_g)$  at  $V_d=50$  mV, where a gate width (W) is 600  $\mu$ m and gate length (L) is 5  $\mu$ m. For single 35 Å HfO<sub>2</sub>, the subthreshold swing is 126 mV/decade, and this value reduces to 83 mV/decade for HfAlO<sub>x</sub>/HfO<sub>2</sub> stacked dielectric with 6 Å HfAlO<sub>x</sub> or 10 Å HfAlO<sub>x</sub>. The gate leakage current is about  $8 \times 10^{-10}$  A for the 10 Å HfAlO<sub>x</sub>/25 Å HfO<sub>2</sub> stacked dielectric and 2  $\times 10^{-8}$  A for single HfO<sub>2</sub> dielectric or 6 Å HfAlO<sub>x</sub>/25 Å HfO<sub>2</sub> gate stacks at  $V_g = 1$  V. We also compared the extrinsic transconductance  $(g_m)$  at  $V_d = 50$  mV of these MOSFETs in Fig. 4(a). The maximum transconductance of 10 Å  $HfAlO_x/25$  Å  $HfO_2$  stacked gate dielectric is two times of the single HfO<sub>2</sub> gate dielectric, and 20% higher than 6 Å  $HfAlO_x/25$  Å  $HfO_2$  stacked gate dielectric. Figure 4(b) plot-

FIG. 4. (Color online) Extrinsic transconductance  $g_m$  versuss  $V_g$  at  $V_d$ =50 mV for InP MOSFETs with 35 Å HfO<sub>2</sub> (a), or 6 Å HfAlO<sub>x</sub>/25 Å HfO<sub>2</sub> (c), or 10 Å HfAlO<sub>x</sub>/25 Å HfO<sub>2</sub> (d) as gate dielectric. (b)  $I_d - V_g$  and  $g_m$  $V_g$  for InP MOSFETs with 10 Å HfAlO<sub>x</sub>/25 Å HfO<sub>2</sub> (d) as gate dielectric at  $V_d$ =2 V (W/L=600 $\mu$ m/5  $\mu$ m).

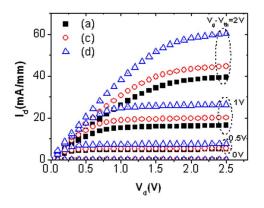

FIG. 5. (Color online)  $I_d - V_d$  as a function of  $V_g$  at  $V_g - V_{th} = 0$ , 0.5 V, 1 V, 2 V for InP MOSFETs with 35 Å HfO<sub>2</sub> (a), or 6 Å HfAlO<sub>x</sub>/25 Å HfO<sub>2</sub> (c), or 10 Å HfAlO<sub>x</sub>/25 Å HfO<sub>2</sub> (d) as gate dielectric (*W*/*L*=600 $\mu$ m/5 $\mu$ m).

ted the  $I_d-V_g$  and  $g_m-V_g$  at  $V_d=2$  V for MOSFETs with 10 Å HfAlO<sub>x</sub>/25 Å HfO<sub>2</sub> stacked gate dielectric. It shows  $V_{\text{th}}$  of about 0.1 V and maximum extrinsic transconductance of 51 mS/mm.

Figure 5 illustrates the  $I_d - V_d$  curves of MOSFETs with different gate stacks at  $V_g = V_{th}$ ,  $V_{th} + 0.5$  V,  $V_{th} + 1$  V, and  $V_{th} + 2$  V. The MOSFETs with 10 Å HfAlO<sub>x</sub>/25 Å HfO<sub>2</sub> stacked dielectric show much higher current driver capability than other types. The driver current density is 60.6, 44.8, and 39.5 mA/mm for 10 Å HfAlO<sub>x</sub>/25 Å HfO<sub>2</sub>, 6 Å HfAlO<sub>x</sub>/25 Å HfO<sub>2</sub>, and 35 Å HfO<sub>2</sub> gate dielectrics at  $V_g$ =  $V_{th} + 2$  V and  $V_d = 2.5$  V, respectively.

In conclusion, MOSCAPs and MOSFETs have been fabricated on InP using various gate stacks deposited by ALD. The MOSCAPs with 10 Å HfAlO<sub>x</sub>/25 Å HfO<sub>2</sub> stacked gate dielectric exhibit EOT of 12 Å, and they also show much better interface with InP substrate than a single 35 Å HfO<sub>2</sub> gate dielectric, demonstrated by 12% less frequency dispersion and one order lower leakage current density. The characteristics of the transistors are also compared; two times higher transconductance, 53% higher drive current density, and 42 mV/decade smaller subthreshold swing are obtained by MOSFETs with 10 Å HfAlO<sub>x</sub>/25 Å HfO<sub>2</sub> gate stack than the ones with single 35 Å HfO<sub>2</sub> gate dielectric. These results suggest that HfAlO<sub>x</sub>/HfO<sub>2</sub> stacked structure holds promise for attaining further scaling down of III-V MOSFETs.

- <sup>1</sup>I. OK, H. Kim, M. Zhang, T. Lee, F. Zhu, L. Yu, S. Koveshnikov, W. Tsai, V. Tokranov, M. Yakimov, S. Oktyabrsky, and J. C. Lee, Proceedings of the IEEE Electron Devices Meeting, 2006 (unpublished).

- <sup>2</sup>H. Kim, I. OK, M. Zhang, F. Zhu, S. Park, J. Yum, H. Zhao, and J. C. Lee, Appl. Phys. Lett. **92**, 032907 (2008).

- <sup>3</sup>F. Ren, M. Hong, W. Hobson, J. Kuo, J. Lothian, J. Mannaerts, J. Lwo, S. Chu, Y. Chen, and A. Cho, Solid-State Electron. **41**, 1751 (1997).

- <sup>4</sup>M. Hong, F. Ren, W. Hobson, J. Kuo, J. Kwo, J. Mannaerts, J. Lothaian, M. Marcus, C. Liu, A. Sergent, T. Lay, and Y. Chen, IEEE International Symposium on Compound Semiconductors, 1998 (unpublished), p. 319.

- <sup>5</sup>Y. Xuan, H. Lin, P. Ye, and G. Wilk, Appl. Phys. Lett. 88, 263518 (2006).

<sup>6</sup>Y. Xuan, Y. Wu, T. Shen, T. Yang, and P. Ye, Proceedings of the IEEE Electron Devices Meeting, 2007 (unpublished), p. 637.

- <sup>7</sup>Y. Xuan, Y. Wu, and P. Ye, IEEE Electron Device Lett. **29**, 294 (2008).

- <sup>8</sup>S. Oktyabrsky, S. Koveshnikov, V. Tokranov, M. Yakimov, R. Kambhampati, H. Bakhru, F. Zhu, J. Lee and W. Tsai, Proceedings of the IEEE 65th Device Research Conference, 2007 (unpublished), p. 203.

- <sup>9</sup>F. Ren, J. Kuo, M. Hong, W. Hobson, J. Lothian, J. Lin, H. Tsai, J. Mannaerts, J. Kwo, S. Chu, Y. Chen, and A. Cho, IEEE Electron Device Lett. **19**, 309 (1998).

- <sup>10</sup>Y. Wu, Y. Xuan, T. Shen, P. D. Ye, Z. Cheng, and A. Lochtefeld, Appl. Phys. Lett. **91**, 022108 (2007).

- <sup>11</sup>Y. Wu, Y. Xuan, P. Ye, Z. Cheng, and A. Lochtefeld, Proceedings of the IEEE 65th Device Research Conference, 2007 (unpublished), p. 117.

- <sup>12</sup>G. Fountain, R. Rudder, A. Hattangady, R. Markunas, and J. Hutchby, Electron Devices Meeting, 1989 (unpublished), P. 887.

- <sup>13</sup>W. Zhu and T. Ma, IEEE Electron Device Lett. **25**, 89 (2004).

- <sup>14</sup>C. Choi, C. Kang, S. Rhee, M. Akbar, S. Krishnan, M. Zhang, H. Kim, T. Lee, I. OK, F. Zhu, and J. Lee, IEEE Electron Device Lett. **26**, 454 (2005).

- <sup>15</sup>P. Ye, G. Wilk, B. Yang, J. Kwo, S. Chu, S. Nakahara, H. Gossmann, J. Mannaerts, M. Hong, K. Ng, and J. Bude, Appl. Phys. Lett. 83, 180 (2003).

- <sup>16</sup>M. Frank, G. Wilk, D. Starodub, T. Gustafsson, E. Garfunkel, Y. Chabal, J. Grazul, and D. Muller, Appl. Phys. Lett. 86, 152904 (2005).

- <sup>17</sup>D. Shahrjerdi, E. Tutuc, and S. Banerjee, Appl. Phys. Lett. **91**, 063501 (2007).

- <sup>18</sup>J. Hauser and K. Ahmed, Proceedings of the AIP International Conference on Characterization Metrology ULSI Technology, 1998 (unpublished), p. 235.